- Electronics

- Xilinx

Reading the memory

I had a think about the reading of the memory and decided that I would use a FIFO to hold a line of data from the RAM, and shift out during the pixel clock. This would have four advantages:

- It would allow me to just keep the CE and OE lines low for the RAM

- All the data will be read at a known time

- When I move over to SDRAM, I'll be able to use burst reads, which would be significantly faster than random acess reads

- If a write operation is in progress when the initial request to read kicks off, it does not need to be aborted, since there's a bit of time until the data is needed

The data for the next line is started to be read during the horizontal back-porch time, and is finished mid-way through the display of the line. There's a bit of logic to read the first line just before the start of the first line, but it's not too complicated.

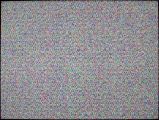

With the RAM effectively initialised to random data (I don't have a way to write to it yet!), the display looks like this:

This worked pretty much first time (I did do a reasonable amount of behavioural simulation), but due to an extra delay in reading the FIFO, the left hand pixel was a little wider than the right hand pixel.

There's a bit of a blur vertically down the screen in the middle, but this is the monitor auto-synching (and not quite getting it right). Sometimes it doesn't appear at all, and once it appeared on the right hand side. I'm not too worried by that at this moment in time.

Note that for this capture, I told the monitor to display it with the correct aspect ratio, rather than extending it (the monitor does 1920x1200; this is 800x600, which means 1600x1200 when scaled up). I'll probably switch to a CRT display I've got (I've also got a small LCD display as well, but that's currently in use elsewhere).

I then added another block RAM as a write FIFO (it contains the address to write, and the contents to write), and extended the FSM to perform writes when it's not reading. However, without anything to control the write, I'll need to come up with some test vectors. It still reads the same though!

I may also use some of the spare bits in the FIFO to allow me to write more than one byte at a time with values. Unfortunately, this may cause problems with the next version which will have a 16-bit data bus (but then I could always use two FIFOs for that).